# A Large-Signal, Analytic Model for the GaAs MESFET

M. ALI KHATIBZADEH, MEMBER, IEEE, AND ROBERT J. TREW, MEMBER, IEEE

**Abstract**—An analytic, large-signal model for the GaAs MESFET is presented. The new device model is physics based and describes the conduction and displacement currents of the FET as a function of instantaneous terminal voltages and their time derivatives. The model allows arbitrary doping profiles in the channel and is thus suitable for the optimization of ion-implanted and buried-channel FET's. It also accounts for charge accumulation in the conducting channel at high electric fields and the associated capacitance in a self-consistent manner. Theoretical predictions of the model are correlated with experimental data on *X*-band power FET's, and excellent agreement is obtained.

## I. INTRODUCTION

THE TECHNOLOGY for producing GaAs monolithic microwave integrated circuits (MMIC's) is rapidly advancing from the research and development stage to production. The development of a computer-aided design (CAD) tool for the key component of this technology, i.e., the GaAs MESFET, is essential. Although significant work has been presented on GaAs MESFET modeling, a unified approach to MESFET modeling in the context of MMIC design is yet to be reported. A MESFET CAD tool suitable for MMIC design and optimization should encompass four features: (1) It should include the effects of process-related device parameters (dimensions, material parameters, doping profile, channel thickness, recess depth, etc.) on the overall performance of the chip. This is especially important since the external fine-tuning or "tweaking" capability utilized in hybrid technology is difficult to employ in MMIC development. Device-circuit interactions play an important role and cannot be ignored. (2) Device models must be computationally efficient on micro- or minicomputers to allow for simulation of FET circuits in an economic fashion. (3) The model must provide the circuit designer with synthesis capability. (4) The device model must have nonlinear capability.

Shockley [1] provided the original FET model applicable to long-gate-length devices operating in a nonsaturated velocity mode. Subsequent models generally fall into four categories: (1) DC and RF small-signal models [2]–[4] which improve Shockley's analysis by including velocity saturation effects and nonuniform donor distribution in the channel. These models suffer from restrictive allowed gate-length to channel-depth ratios and unrealistic calcu-

lated drain-source resistance values. (2) Numerical models [5]–[8] which solve the fundamental, nonlinear, coupled partial differential equations of the device using finite-difference or finite-element numerical techniques. These models are important for understanding the device physics but are computationally inefficient for RF circuit simulations. Some work on large-signal RF circuit simulations using numerical models has been reported [9]. (3) Empirical and semiempirical models [10]–[12] which rely on parameter extraction from measured dc and/or RF small-signal *S* parameters. These models have a high degree of computational efficiency and can be easily implemented in circuit simulators and are very popular among circuit designers. However, since the device must be fabricated before the model can be determined, this approach is not ideal for studying the effects of process-related FET parameters on the overall performance of the circuit. (4) Large-signal analytic models [13]–[14] which attempt to solve the fundamental device equations with a minimum number of simplifying assumptions. These models try to bridge the gap between numerical models and circuit-simulation-oriented empirical models. This type of model is ideal for design optimization studies since the device need not be fabricated before it can be investigated.

There are three effects that must be included in the analytic models in order to establish an accurate description of device performance: (1) The "velocity vector rotation" phenomenon [13], which refers to the rotation of the velocity vector toward the drain electrode with increasing drain-source voltage, must be considered. This will improve the accuracy of the calculated output resistance. This phenomenon has been confirmed in numerical simulations [14]. (2) The "abrupt depletion approximation" must be removed. (3) Local charge neutrality in the conducting channel is not maintained. Numerical simulations [14] have shown that there is a charge buildup in the channel at large drain-source voltages and short gate lengths, i.e., at large electric fields. Madjar *et al.* [15], [16] have shown that excess carrier charge at the drain electrode must be included in order to obtain a continuous potential solution, although their approach to this problem is empirical. The magnitude of this accumulation should be a function of the field structure and device parameters. A comprehensive model requires that the charge domain be analytically characterized.

In this paper, a new large-signal, analytic model for the GaAs MESFET is presented. The new model has the novel

Manuscript received April 24, 1987; revised September 11, 1987.

The authors are with the Electrical and Computer Engineering Department, North Carolina State University, Raleigh, NC 27695-7911.

IEEE Log Number 8717976.

features that arbitrary doping profiles are allowed and charge accumulation or depletion in the conducting channel is modeled in a simple fashion. The inclusion and physical description of the charge domain permit a true large-signal, analytic MESFET model to be developed. It is known that for short-gate-length devices, due to the increase in the electric field, electrons accumulate near the drain end of the gate. The magnitude of this charge and the capacitance associated with it are calculated by this model in a self-consistent manner for the first time.

Theoretical results of this model are correlated with experimental data on Raytheon X-band power FET's. DC and RF small-signal parameters calculated with the model are compared with similar parameters extracted from measured data at different bias voltages. The harmonic balance method [17] is used to simulate the output power and power-added efficiency of these power FET's in RF circuits at large drive levels. Excellent agreement between the modeled and measured results is obtained. The new model permits the systematic investigation of RF performance due to parameter variations [18]. In this context the model is very useful for process simulation studies, as well as RF design applications [19].

## II. THE DEVICE MODEL

### A. Model Formulation

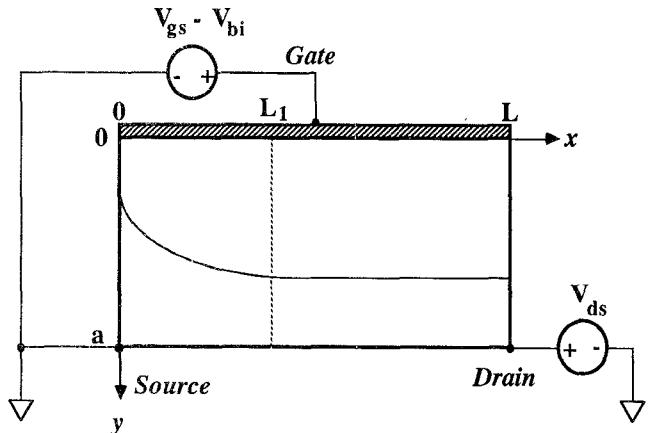

The active or "intrinsic" region of an FET is shown in Fig. 1. This region consists of the area of the channel directly under the gate electrode. The model is formulated around this region. All other regions of the device are modeled phenomenologically using external linear elements. The applicable device equations are

$$\nabla^2 \Psi = -\frac{q}{\epsilon} [N(y) - n(x, y)] \quad (1)$$

$$\bar{J} = -q n \bar{v} + q D \nabla n \quad (2)$$

$$\nabla \cdot \bar{J} = q \frac{\partial n}{\partial t} \quad (3)$$

and

$$\bar{J}_t = \bar{J} + \epsilon \frac{\partial \bar{E}}{\partial t} \quad (4)$$

where

$$\bar{E} = -\nabla \Psi \quad (5)$$

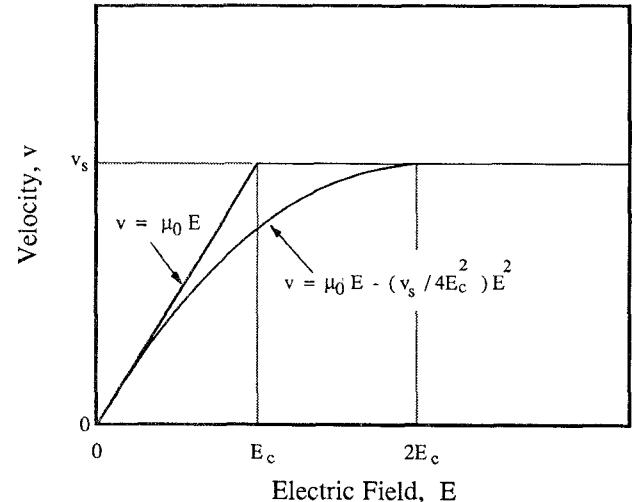

is the electric field,  $\psi$  is the electrostatic potential,  $N$  is the arbitrary donor concentration in the channel,  $n$  is the free-electron density,  $\bar{v}$  is the electron velocity,  $D$  is the diffusion coefficient,  $\bar{J}$  is the conduction current density (drift + diffusion), and  $\bar{J}_t$  is the total current density (conduction + displacement). It is assumed that  $\bar{v}$  and  $\bar{E}$  are codirectional, i.e.,  $\bar{v} = -\mu(E)\bar{E}$ , where  $\mu(E)$  is the field-dependent mobility. The formulation of the model is independent of the functional form of the  $v-E$  characteristic and  $v-E$  characteristics including negative differential mobility regions can be utilized. In this work, however, the saturating  $v-E$  characteristic shown in Fig. 2 is used. This

Fig. 1. Active region of an FET used in the model.

Fig. 2. Velocity field characteristic used in the model.

$v-E$  characteristic has been found to produce accurate results for most practical applications. Based upon the magnitude of the electric field in the channel, specifically at the  $y = a$  boundary ( $E(x, a)$ ), the device can operate in one of three modes:

$$E(0, a) < E(L, a) < E_c \quad (\text{mode-A})$$

$$E(0, a) < E(L_1, a) = E_c < E(L, a) \quad (\text{mode-B})$$

$$E_c < E(0, a) < E(L, a). \quad (\text{mode-C})$$

The plane  $x = L_1$  indicated in Fig. 1 separates the saturation and linear regions of the device. The source and drain currents are calculated by integrating  $\bar{J}$  over the entire  $x = 0$  and  $x = L$  boundary planes, respectively. The gate contact ( $y = 0$ ) is modeled as an ideal constant potential boundary while the substrate interface ( $y = a$ ) is treated as an ideal reflecting boundary.

Since (1)–(3) are coupled together, a functional form for  $n(x, y)$  is assumed *a priori* in order to solve for  $\Psi$  analytically. In general,  $n$  must vary continuously from almost zero near the gate ( $y \approx 0$ ) to a value almost equal to the background doping concentration in the channel ( $y \approx a$ ). In order to produce a smooth transition for an

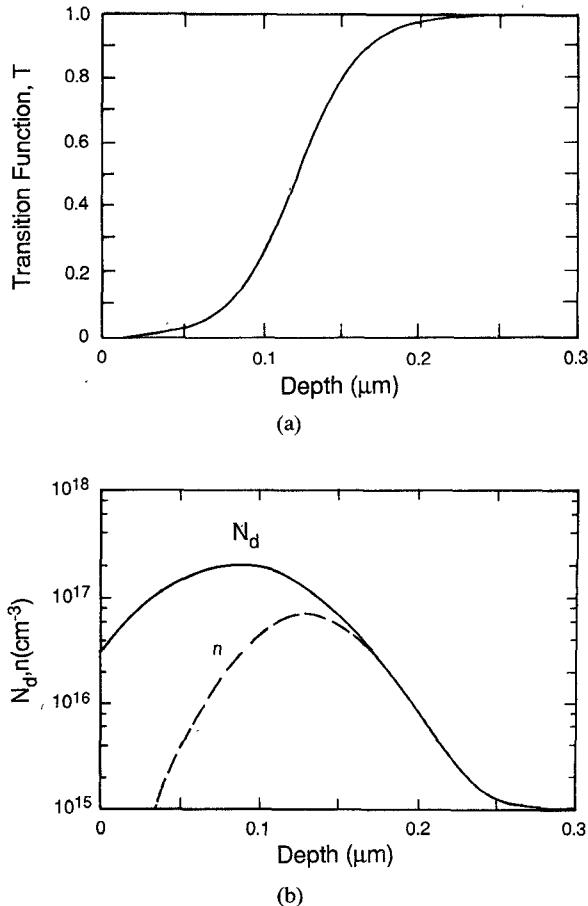

Fig. 3. (a) Transition function and (b) free electron distribution of an ion-implanted FET.

arbitrary doping profile, the following functional form for  $n(x, y)$  is assumed:

$$n(x, y) = [1 + \gamma(x - L_1)] T(d(x), y) N(y) \quad (6)$$

where  $T(d(x), y)$  is a *transition function* and is defined as

$$T(d(x), y) \equiv 1 - \frac{1}{1 + \exp\left[\frac{y - d(x)}{\lambda}\right]}. \quad (7)$$

The term  $[1 + \gamma(x - L_1)]$  allows for charge accumulation or depletion in the channel. As will be shown, the excess charge in the channel allows for a self-consistent solution of the Poisson equation in the saturation region ( $L_1 < x \leq L$ ). For  $x \leq L_1$  (i.e., the linear region),  $\gamma = 0$ . Whether accumulation or depletion occurs in the channel will depend on the sign of  $\gamma$ , which is determined from the solution of  $\Psi$  in the saturation region. In the Yamaguchi-Kodera model [13], only the  $\gamma < 0$  case was allowed.

In the linear region (i.e.,  $x \leq L_1$ ,  $\gamma = 0$ ), at  $y = d(x)$  the carrier concentration is 50 percent of the background doping. Therefore,  $d(x)$  can be thought of as an "effective depletion-layer width." Fig. 3(a) shows the variation of  $T$  with  $y$  for a typical device and gate-bias condition. Fig. 3(b) shows the carrier concentration corresponding to an ion-implanted profile as obtained from (6). For  $y \ll d(x)$ ,  $T \approx 0$  and therefore  $n \approx 0$ . For  $y \gg d(x)$ ,  $T \approx 1$  and  $n \approx N$ .

This formulation ignores the out-diffusion of carriers into the substrate. If one defines the "transition region" between depletion and channel as the region where  $n$  varies from 5 percent to 95 percent of  $N$ , from (6) and (7) it immediately follows that this corresponds to  $d - 3\lambda \leq y \leq d + 3\lambda$ . Thus the width of the "transition" region is  $6\lambda$ . Numerical simulations [13] show that this region usually extends to about  $6\lambda_D$ , where  $\lambda_D$  is the Debye length. Therefore,  $\lambda$  must be of the order of the Debye length.

### B. Solution for The Potential $\Psi$

Yamaguchi *et al.* [13] showed that the solution to (1) can be represented by a linear superposition of two components, i.e.,  $\Psi = \Psi_0 + \Psi_1$ , where  $\Psi_0$  is the Laplacian potential due to the impressed voltages on the electrodes and  $\Psi_1$  is due to the space charge in the channel and satisfies the Poisson's equation. In mathematical terms,

$$\nabla^2 \Psi_0 = 0 \quad (8)$$

with boundary conditions

$$\Psi_0(0, a) = 0 \quad (9a)$$

$$\Psi_0(L, a) = V_0 \quad (9b)$$

$$\frac{\partial \Psi_0}{\partial y}(x, a) = 0 \quad (9c)$$

$$\Psi_0(x, 0) = 0 \quad (9d)$$

and

$$\nabla^2 \Psi_1 = -\frac{q}{\epsilon}(N - n) \quad (10)$$

with boundary conditions

$$\Psi_1(0, a) = 0 \quad (11a)$$

$$\Psi_1(L, a) = V_1 \quad (11b)$$

$$\frac{\partial \Psi_1}{\partial y}(x, a) = 0 \quad (11c)$$

$$\Psi_1(x, 0) = V_{gs} - V_{bi} \quad (11d)$$

where  $V_{bi}$  is the built-in voltage of the gate Shottky contact, and  $V_{gs}$  and  $V_{ds} = V_1 + V_0$  are the applied gate-source and drain-source voltages across the intrinsic FET, respectively. The solution to (8) with boundary conditions (9a)–(9d) is

$$\Psi_0(x, y) = \sum_{j=0}^{\infty} A_j \sinh\left[\frac{(2j+1)\pi}{2a}x\right] \sin\left[\frac{(2j+1)\pi}{2a}y\right] \quad (12)$$

where

$$A_j = \frac{4V_0}{(2j+1)\pi \sinh\left[\frac{(2j+1)\pi L}{2a}\right]} \quad (j = 0, 1, \dots).$$

For most FET's  $L/a \geq 1$ ; therefore  $A_j$  converges rapidly and it is sufficient to consider the first term only. By doing so, however,  $\Psi_0$  will no longer satisfy boundary condition

(9b). Thus to preserve the boundary condition, one must reapply (9b) to the first term in equation (12) to get

$$\Psi_0(x, y) = \frac{V_0}{\sinh\left(\frac{\pi L}{2a}\right)} \sinh\left(\frac{\pi x}{2a}\right) \sin\left(\frac{\pi y}{2a}\right). \quad (13)$$

The solution for  $\Psi_1$  depends on the carrier concentration  $n$ . Using definitions (6) and (7),  $\Psi_1$  can be determined assuming  $|\partial^2\Psi_1/\partial y^2|$  dominates  $|\partial^2\Psi_1/\partial x^2|$ . For  $0 \leq x \leq L_1$ , we get

$$\begin{aligned} \Psi_1(x, y) = & -\frac{q}{\epsilon} \int_y^a \int_{y'}^a [1 - T(d(x), y'')] N(y'') dy'' dy' \\ & \cdot N(y'') dy'' dy' + \frac{V_1}{L} x. \end{aligned} \quad (14)$$

For  $L_1 < x \leq L$  ( $d(x) \equiv d_1$ ), the solution is

$$\begin{aligned} \Psi_1(x, y) = & -\frac{q}{\epsilon} \int_y^a \int_{y'}^a [1 - T(d_1, y'')] N(y'') dy'' dy' \\ & + \frac{V_1}{L} x + \frac{q}{\epsilon} \gamma(x - L_1) \\ & \cdot \int_y^a \int_{y'}^a T(d_1, y'') N(y'') dy'' dy'. \end{aligned} \quad (15)$$

The last term in (15) is the potential due to the accumulation or depletion charge. For  $x \leq L_1$ , the "depletion-layer width"  $d$  varies as a function of  $x$ . To solve for  $d(x)$ , we must apply condition (11d) to (14). The result is an implicit solution for  $d(x)$  of the form

$$-\frac{q}{\epsilon} F_1(d(x)) + \frac{V_1}{L} x = V_{gs} - V_{bi} \quad (x \leq L_1) \quad (16)$$

where

$$F_1(d) \equiv \int_0^a \int_{y'}^a [1 - T(d, y'')] N(y'') dy'' dy'.$$

It can be shown that for the special case of uniform doping ( $N(y) \approx N_0$ ) and using the abrupt depletion approximation ( $\lambda \rightarrow 0$ ),  $F_1(d)$  reduces to  $N_0 d^2$  and  $d(x)$  can be solved for explicitly to yield the expected result

$$d(x) = \sqrt{\left(\frac{2\epsilon}{qN_0}\right) \left(\frac{V_1}{L} x - V_{gs} + V_{bi}\right)}.$$

In general, however,  $F_1(d)$  depends on the arbitrary doping profile and cannot be calculated analytically. Instead, for a given doping profile,  $F_1(d)$  is tabulated numerically as a function of  $d$  for 60 values of  $d$  in the interval  $[0, 2a]$ . Then for any given values of  $V_{gs}$  and  $x$ , the corresponding value of  $F_1(d)$  can be calculated from (16) and cubic spline interpolation can be used on the tabulated numbers to get  $d(x)$ . This procedure is computationally very efficient and accurate.

The pinch-off voltage  $V_{po}$  is defined as the gate-source voltage for which the channel is completely pinched off at the source side ( $x = 0$ ). That is at  $V_{gs} = V_{po}$ ,  $d(0) \rightarrow \infty$  which implies  $n(0, y) \rightarrow 0$ . From (16), we can write  $V_{po}$  as

$$V_{po} = V_{bi} - \frac{q}{\epsilon} \int_0^a \int_{y'}^a N(y'') dy'' dy'. \quad (17)$$

For  $L_1 \leq x \leq L$ ,  $d(x) \equiv d_1$ , where  $d_1$  is found by substituting  $x = L_1$  in (16). Applying condition (11d) to (15) yields

$$\begin{aligned} -\frac{q}{\epsilon} F_1(d_1) + \frac{V_1}{L} x + \frac{q}{\epsilon} \gamma(x - L_1) F_2(d_1) = & V_{gs} - V_{bi} \\ (L_1 \leq x \leq L) \end{aligned} \quad (18)$$

where

$$F_2(d) \equiv \int_0^a \int_{y'}^a T(d, y'') N(y'') dy'' dy'.$$

From the definitions of  $V_{po}$  and  $F_1(d)$ , it follows that

$$F_2(d) = -\frac{\epsilon}{q} (V_{po} - V_{bi}) - F_1(d). \quad (19)$$

Thus additional integration is not required for the calculation of  $F_2(d)$ . Equation (18) must hold for all  $L_1 \leq x \leq L$ ; therefore

$$\gamma = \frac{-\epsilon V_1}{q L F_2(d_1)}. \quad (20)$$

Equation (20) gives the solution for the slope of the carrier concentration in the saturation region. For  $\gamma < 0$  ( $V_1 > 0$ ), charge depletion in the channel occurs, whereas for  $\gamma > 0$  ( $V_1 < 0$ ) accumulation results. The solution for  $V_1$  will arise from the current continuity equation. The effect of the extra charge in the channel is to enable  $\Psi$  to satisfy the potential boundary condition (11d) while the depletion-layer width is held constant in the saturation region.

### C. Drain Current

In order to solve for the current, the electric field distribution in the device is calculated. The electric field has two components: one due to  $\Psi_0$  and the other due to  $\Psi_1$ . The  $x$  component of the electric field in both the linear and saturation regions can be approximated by

$$\begin{aligned} E_x(x, y) = & -\frac{V_1}{L} \left[ 1 - \left( \frac{y}{a} - 1 \right)^2 \right] \\ & - \xi \cosh\left(\frac{\pi x}{2a}\right) \sin\left(\frac{\pi y}{2a}\right) \frac{V_0}{L} \end{aligned} \quad (21)$$

where

$$\xi \equiv \frac{\frac{\pi L}{2a}}{\sinh\left(\frac{\pi L}{2a}\right)}$$

and the second-order Taylor's expansion of the original function about  $y = a$  is utilized. At the substrate interface ( $y = a$ ), the magnitude of the electric field becomes

$$\begin{aligned} E(x, a) &= |E_x(x, a)| \\ &= \frac{V_1}{L} + \xi \frac{V_0}{L} \cosh\left(\frac{\pi x}{2a}\right). \end{aligned} \quad (22)$$

By definition of the plane  $x = L_1$ ,  $E(L_1, a) = E_c$ . Combining this with (22) and solving for  $L_1$  yields

$$L_1 = \left(\frac{2a}{\pi}\right) \ln\left[\eta + \sqrt{\eta^2 - 1}\right] \quad (23)$$

where

$$\eta \equiv \left(\frac{2a}{\pi L}\right) \left(\frac{E_c L - V_1}{V_0}\right) \sinh\left(\frac{\pi L}{2a}\right). \quad (24)$$

Thus given  $V_{ds}$  and  $V_1$ ,  $L_1$  can be explicitly determined.

To calculate the current, the conduction current density as given by (2) is integrated. In the linear region ( $x \leq L_1$ ), there is no  $x$  dependence of the carrier concentration; therefore, only the drift component of  $\bar{J}$  is considered. In the saturation region, however, the diffusion term must also be included. The details of the calculations of the source and drain currents are described elsewhere [20]. In general, the source and drain currents can be written in the following forms:

$$I_s = A V_1 + B \quad (25)$$

$$I_d = A' V_1 + B' \quad (26)$$

where  $A, A', B, B'$  are nonlinear functions of  $V_1$  and device parameters. Following the "quasi-static" approach of Yamaguchi *et al.* [13], i.e.,  $\partial n / \partial t = 0$ , in (3) and neglecting the current through the gate contact, the current continuity condition (3) reduces to  $I_s = I_d$ . In the model, the Newton-Raphson method is used to calculate the root of the equation  $f(V_1) = I_d - I_s = 0$ .

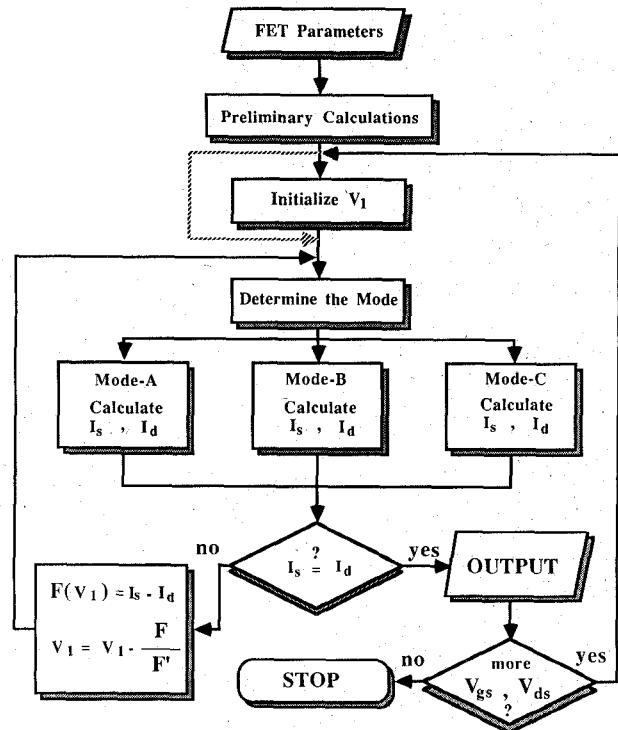

Fig. 4 shows the algorithm for the model. Starting with material and device parameters, a set of preliminary calculations is done as represented by the INITIAL block. These calculations involve the tabulation of  $F_1(d)$  and three other doping-profile-dependent integrals used in the model for 60 values of  $d$ . The INITIAL step takes about 30 seconds of CPU time on a Microvax-II computer. This step is done once for a particular device and need not be repeated. Following the INITIAL step, given a set of bias voltages, the solution for  $V_1$  is found using Newton's method. An approximate analytic solution for  $V_1$  is used as the initial value. The solution for  $V_1$  takes about 2-4 iterations to converge to a relative error of  $10^{-4}$  for the currents  $I_s$  and  $I_d$ . Once  $V_1$  is found, all parameters of the

Fig. 4. Algorithm for the FET model.

TABLE I

DEVICE PARAMETERS

| Parameter                   | (Unit)                     | Value             |

|-----------------------------|----------------------------|-------------------|

| Gate Length                 | ( $\mu\text{m}$ )          | 0.56              |

| Gate Width                  | ( $\mu\text{m}$ )          | 1200              |

| Channel Thickness           | ( $\mu\text{m}$ )          | 0.35              |

| Recess Depth                | ( $\mu\text{m}$ )          | 0                 |

| Gate Resistance             | ( $\mu\text{m}$ )          | 0.4               |

| Source Resistance           | ( $\mu\text{m}$ )          | 0.8               |

| Drain Resistance            | ( $\mu\text{m}$ )          | 0.8               |

| Gate Inductance             | (nH)                       | 0.08              |

| Source Inductance           | (nH)                       | 0.08              |

| Drain Inductance            | (nH)                       | 0.08              |

| Saturation Velocity         | cm/sec                     | $1.5 \times 10^7$ |

| Low-Field Mobility          | $\text{cm}^2/\text{V.sec}$ | 4000              |

| High-Field Diffusion Coeff. | $\text{cm}^2/\text{sec}$   | 10                |

| Critical Field              | kV/cm                      | 3.75              |

| Break-Down Voltage          | V                          | 20                |

| Gate Schottky               | V                          | 0.70              |

| Built-in Voltage            |                            |                   |

model are calculated. The gate and drain displacement currents are related to the time derivatives of  $V_{gs}$  and  $V_{ds}$  through the capacitance matrix [15], [16]

$$\begin{bmatrix} i_g \\ i_d \end{bmatrix} = \begin{bmatrix} C_{11} & C_{12} \\ C_{21} & C_{22} \end{bmatrix} \cdot \frac{\partial}{\partial t} \begin{bmatrix} V_{gs} \\ V_{ds} \end{bmatrix} \quad (27)$$

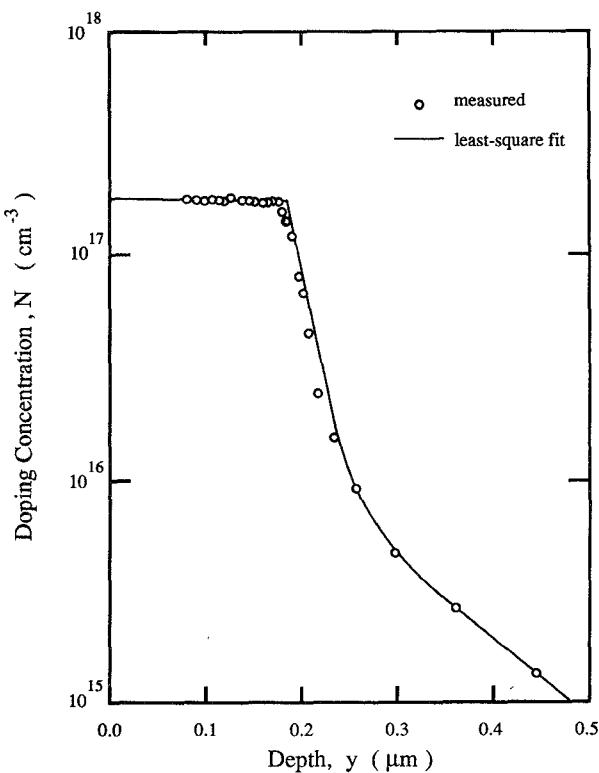

Fig. 5. Experimental and modeled donor profiles for a Raytheon power FET.

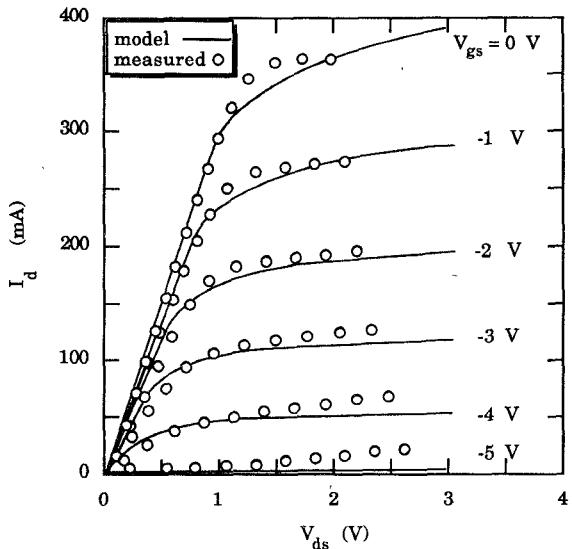

Fig. 6. Measured and modeled  $I$ - $V$  characteristics for the Raytheon ion-implanted GaAs FET.

where the capacitance matrix is in general nonsymmetric. External shunt diodes (nonlinear resistors) are used to model gate-drain breakdown and forward-biased gate leakage currents. For a given set of bias voltages, the calculation of all parameters takes about 32 milliseconds total CPU time on a Microvax-II computer.

### III. SIMULATION RESULTS

The model is used in conjunction with the method of harmonic balance [17] to study the large-signal performance of RF circuits. The NCSU harmonic balance analy-

Fig. 7. Calculated and measured (a) small-signal transconductance and (b) small-signal gate-source capacitance.

sis program can, in general, be used to study single FET circuits such as single-stage amplifiers, feedback amplifiers, and doublers. Table I shows the parameters of an experimental  $X$ -band power FET. The measured  $C$ - $V$  profile and the analytic, least-square fit to the doping profile which was input to the model is shown in Fig. 5. The measured and calculated static  $I$ - $V$  characteristics of the FET are shown in Fig. 6. The calculated small-signal parameters of the device were compared with those extracted from measured  $S$  parameters in the 2–18 GHz frequency range. The most important nonlinear elements

(a)

(b)

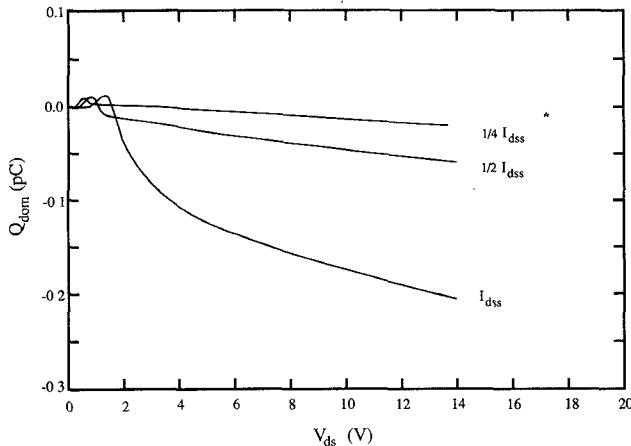

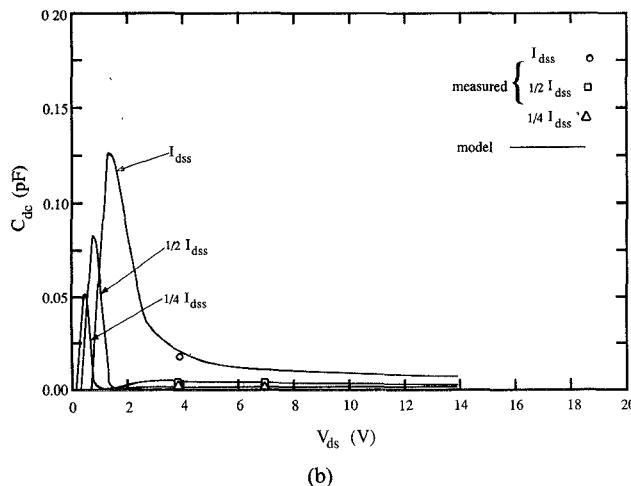

Fig. 8. (a) Calculated channel domain charge. (b) Calculated channel domain capacitance.

$g_m$  and  $C_{gs}$  are shown in Fig. 7 as a function of  $V_{gs}$  at  $V_{ds} = 4.0$  V. A sharp drop in the gate-source capacitance occurs near the pinch-off voltage due to the cutoff of the channel. Beyond pinch-off, the only contribution to  $C_{gs}$  comes from the fringing capacitances due to the charges distributed beyond the gate edges.

Fig. 8(a) shows the excess charge in the channel. For small drain-source voltages, slight depletion ( $Q_{\text{dom}} > 0$ ) near the drain is observed. At large drain-source voltages and small  $V_{gs}$ , accumulation ( $Q_{\text{dom}} < 0$ ) is observed instead. The accumulated charge has a capacitance associated with it, indicated as  $C_{dc}$  (domain feedback capacitance). To our knowledge, this is the first analytic calculation of this capacitance. Fig. 8(b) shows the calculated and measured  $C_{dc}$  versus  $V_{ds}$  for three gate-bias conditions. Good agreement between the model predictions and experimental data is obtained.

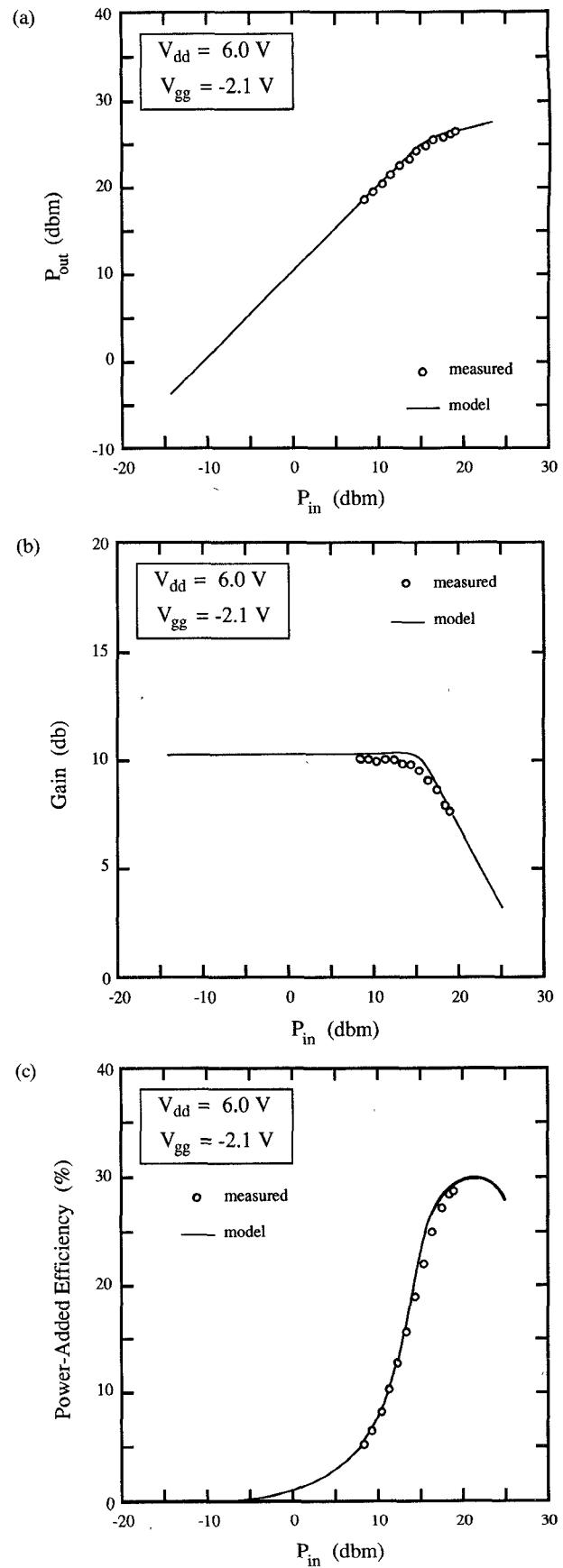

Using the harmonic balance simulator, the large-signal performance of the power FET's at X-band (10 GHz) has been calculated. Fig. 9(a) shows the output power at the fundamental frequency versus the input power at the bias condition of  $V_{ds} = 6.0$  V and  $V_{gs} = -2.10$  V ( $I_d = 200$  mA). The calculated small-signal gain of the device was

Fig. 9. (a) Calculated and measured  $P_{\text{out}}$  versus  $P_{\text{in}}$  for the Raytheon ion-implanted GaAs FET ( $W = 1.2$  mm,  $L_g = 0.5$   $\mu\text{m}$ ,  $f = 10$  GHz,  $V_{ds} = 6$  V,  $V_{gs} = -2.1$  V). (b) Calculated and measured gain versus  $P_{\text{in}}$ . (c) Calculated and measured power-added efficiency versus  $P_{\text{in}}$ .

10.3 dB, which agrees well with the measured gain of 10 dB, as shown in Fig. 9(b). The output power at the 1-dB gain compression point is shown to be about 27 dBm. The power-added efficiency versus input power is shown in Fig. 9(c). The measured maximum power-added efficiency is 28 percent which agrees well with the calculated value of 30 percent. It should be noted that these results were obtained with no parameter adjustments once the device doping profile and geometry were determined.

#### IV. CONCLUSIONS

A new physics based large-signal analytic model for the GaAs MESFET has been presented. The new model allows for arbitrary doping profiles, and considers the effects of such nonuniform doping profiles on the nonlinearities of the FET. The model also takes into account the accumulation of charge in the channel at large drain-source voltages in a manner consistent with the Poisson and current continuity equations. The model accepts as input data device geometry, material parameters, bias, and RF operation conditions. It returns small- and large-signal RF performance including output power, gain, efficiency, harmonic content, and impedances. DC, RF small-signal and large-signal parameters of Raytheon 1.2 mm *X*-band power FET's have been calculated and compared with measured values. Excellent agreement between the theoretical and experimental results is obtained. The model is useful in both device and circuit design optimization applications.

#### ACKNOWLEDGMENT

The authors wish to thank Raytheon for supplying the experimental data used in this work, and H. Willing of the U.S. Army Strategic Defense Command for his support and encouragement.

#### REFERENCES

- 1] W. Shockley, "A unipolar 'field-effect' transistor," *Proc. IRE*, vol. 40, pp. 1365-1376, Nov. 1952.

- 2] A. B. Grebene and S. K. Ghandhi, "General theory for pinched operation of the junction-gate FET," *Solid-State Electron.*, vol. 12, pp. 573-589, 1969.

- 3] K. Lebovec and R. Zuleeg, "Voltage-current characteristics of GaAs J-FETs in the hot electron range," *Solid-State Electron.*, vol. 13, pp. 1415-1426, 1970.

- 4] R. Puccel, H. Haus, and M. Statz, "Signal and noise properties of gallium arsenide microwave field-effect transistors," in *Advances in Electronics and Electron Physics*, vol. 38. New York: Academic Press, 1975, pp. 195-205.

- 5] D. P. Kennedy and R. R. O'Brien, "Computer aided two dimensional analysis of the junction field-effect transistor," *IBM J. Res. Develop.*, pp. 95-116, Mar. 1970.

- 6] M. Reiser, "A two-dimensional numerical FET model for dc, ac, and large-signal analysis," *IEEE Trans. Electron Devices*, vol. ED-20, pp. 34-45, Jan. 1973.

- 7] H. L. Grubin, "Large-signal numerical simulation of field-effect transistors," presented at the Sixth Biennial Conf. on Active Microwave Semiconductor Devices and Circuits, Cornell University, Ithaca, NY, Aug. 16-19, 1977.

- 8] C. M. Snowden and D. Loret, "Two-dimensional hot-electron models for short-gate-length GaAs MESFET's," *IEEE Trans. Electron Devices*, vol. ED-34, pp. 212-223, Feb. 1987.

- 9] C. M. Snowden, M. J. Howes, and D. V. Morgan, "Large-signal modeling of GaAs MESFET operation," *IEEE Trans. Electron Devices*, vol. ED-30, pp. 1817-1824, Dec. 1983.

- [10] H. A. Willing, C. Raucher, and P. DeSantis, "A technique for predicting large-signal performance of a GaAs MESFET," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-26, pp. 1017-1023, Dec. 1978.

- [11] W. R. Curtice and M. Ettenberg, "A non-linear GaAs FET model for use in the design of output circuits for power amplifiers," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-33, pp. 1383-1394, Dec. 1985.

- [12] J. M. Golio, J. R. Hauser, and P. A. Blakey, "A large-signal GaAs MESFET model implemented on SPICE," *IEEE Circuits and Devices Magazine*, pp. 21-30, Sept. 1985.

- [13] K. Yamaguchi and M. Kodera, "Drain conductance of junction gate FET's in the hot electron range," *IEEE Trans. Electron Devices*, vol. ED-23, pp. 545-553, June 1976.

- [14] T. Wada and J. Frey, "Physical basis for short-channel MESFET operation," *IEEE Trans. Electron Devices*, vol. ED-26, pp. 476-490, Apr. 1979.

- [15] A. Madjar and F. J. Rosenbaum, "A large-signal model for the GaAs MESFET," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-29, pp. 781-788, Aug. 1981.

- [16] A. Madjar and F. J. Rosenbaum, "An ac large-signal model for the GaAs MESFET," Rep. N00014-78-C-0256, Washington University, St. Louis, MO, Aug. 1979.

- [17] V. Rizzoli, A. Lipparini, and E. Marazzi, "A general purpose program for nonlinear microwave circuit design," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-31, pp. 762-770, Sept. 1983.

- [18] M. A. Khatibzadeh and R. J. Trew, "Sensitivity of the RF performance of GaAs power FET's to process-dependent parameters," presented at the 1987 IEEE/Cornell Conference on Advanced Concepts in High-Speed Semiconductor Devices and Circuits.

- [19] M. A. Khatibzadeh, R. J. Trew, and I. J. Bahl, "Large-signal modeling of GaAs power FET amplifiers," in *1987 IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 107-110.

- [20] M. A. Khatibzadeh, "Large-signal modeling of gallium-arsenide field-effect transistors," Ph.D. dissertation, North Carolina State University, 1987.

**M. Ali Khatibzadeh** (S'81-M'87) was born in Tehran, Iran, on April 4, 1960. He received the B.S., M.S., and Ph.D. degrees, all in electrical engineering, from North Carolina State University in 1982, 1984, and 1987, respectively. His dissertation research concerned the large-signal modeling of GaAs MESFET's for microwave analog applications.

In 1987, he joined the Central Research Laboratories, Texas Instruments, where he is presently involved in the research and development of heterojunction bipolar transistors and monolithic millimeter-wave integrated circuits.

**Robert J. Trew** (S'71-M'74) was born in Saginaw, MI, in 1944. He received the B.E.E. degree from the General Motors Institute, Flint, MI, in 1968 and the M.S.E. and Ph.D. degrees from the University of Michigan, Ann Arbor, in 1969 and 1975, respectively.

From 1975 to 1977 he was employed by the Watkins-Johnson Company, Palo Alto, CA, where he was involved in the design and development of various types of microwave components, including the first reported octave band YIG tuned GaAs MESFET oscillator. In 1977 he joined the faculty of North Carolina State University, Raleigh, where he is now a Professor. His interests are in the areas of computer-aided design and experimental characterization of microwave solid-state devices.

Dr. Trew is a member of Eta Kappa Nu, Sigma Xi, and Tau Beta Pi.